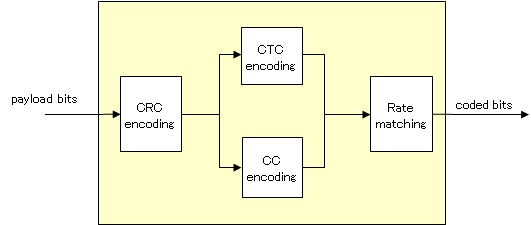

TC1750は高スループットのターボ・畳み込み符号エンコーダです。LTE, HSPA+, WiMAX 16e/mなどに対応します。畳み込みターボ符号 (CTC) エンコード、または畳み込み符号 (CC) エンコードのいずれかと、上記3つのPHYレイヤ仕様に沿ったレートマッチングを実行します。

レートマッチングは状況に合わせた動作が可能で、HARQを実行するために簡単に利用できます。TC1750はスループットの高い構成のため、1コアのインスタンスでマルチGbits/sレベルのスループットに到達できます。

LTEモードでペイロードレートは最大4 Gbits/s (クロック周波数500 MHz)

HSPAモードでペイロードレートは最大1 Gbits/s (クロック周波数500 MHz)

TC1750はアップリンクとダウンリンク両方で利用可能です。基地局 (フェムトセルから大基地局まで) や端末のSoCにインプリメントできます。ASIC用コアとFPGA用コアがあります。

● 機能的仕様

このIPコアは単なるターボエンコーダのアクセラレータではなく、レートマッチング機能 (下記参照) もサポートし、それによりハードウェアモジュールを追加することなくDSPからこのタスクを解放します。

- 3GPP LTEモード

- CRCの符号化

- CTCのブロックサイズ範囲: 40~6144ビット

- CCのブロックサイズ: 8~1024ビット

- レートマッチング: ビットコレクション, サブブロックのインタリーブ, ビット選択

- 3GPP-HSPA+ モード

- CTCのブロックサイズ範囲: 40~5114ビット

- CCのブロックサイズ範囲: 8~504ビット

- レートマッチング: ビット分割, パンクチャ / 反復, ビットコレクション

- IEEE802.16d/e/m WiMAX モード

- CRCの符号化

- CTCのブロックサイズ範囲: 48~4800ビット

- CCのブロックサイズ範囲: 48~288ビット

- レートマッチング: サブブロックのインタリーブ, ビットグルーピング, ビット選択

● 機能

- ブロックごとに物理レイヤモード、ブロック長、レートマッチングパラメータ変更

- バンクスワッピングによりレイテンシ軽減

- 外部メモリ不要

- 高スループットのアーキテクチャ

- シリコン実証済み

- ASICコア: Verilog または VHDLのRTLソースコード

- FPGAコア: アルテラ、ザイリンクス、ラティスの主要デバイスにインプリメント可能