## XIP3030H: SHA-3

# A High-Speed Versatile Core for SHA-3-224/256/384/512 and (c)SHAKE-128/256

Datasheet ver. 1.0 October 31, 2022

info@xiphera.com

#### Introduction

XIP3030H is a high-speed IP core designed for versatile support of all variants of the SHA-3 hash function and related extendable-output function SHAKE as well as the SHA-3 derived function cSHAKE and its variants KMAC, TupleHash and ParallelHash (including their arbitrary-length output variants). SHA-3 and SHAKE are defined in the NIST (National Institute of Standards and Technology) standard FIPS PUB 202 [1] and cSHAKE, KMAC, TupleHash and ParallelHash are specified in NIST Special Publication 800-185 [2]. Because of the versatile algorithm support, XIP3030H can be used in various applications that require SHA-3 hashing or other supported SHA-3 based functionalities. XIP3030H is optimized for maximum speed and is optimal for applications that require high-speed hashing. SHA-3 plays a central role also in post-quantum cryptography schemes. The design is device-agnostic and fully compliant with various FPGA platforms. XIP3030H offers high level of implementation security and is fully protected against timing attacks as its execution time does not depend on the values of the inputs.

The interface of XIP3030H is pin-wise compatible with XIP3030C, the compact versatile SHA-3 core with the same functionalities. The only differences are in performance (latency) and resource requirements. XIP3030H has been designed for easy integration with FPGA- and ASIC-based designs in a vendor-agnostic design methodology, and the functionality of XIP3030H does not rely on any FPGA manufacturer-specific features.

## **Key Features**

• **High Throughput:** XIP3030H offers very high throughput with high maximum clock frequency. XIP3030H achieves peak throughputs of several of Gbps depending on the target FPGA.

XIP3030H: SHA-3 Datasheet, ver. 1.0

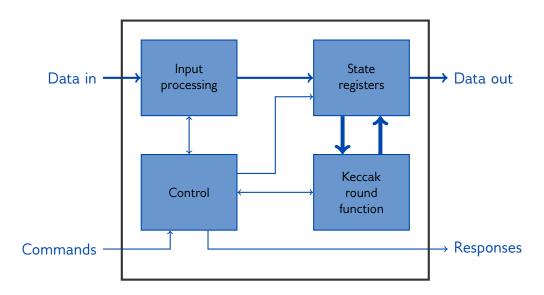

Figure 1: Internal high-level block diagram of XIP3030H

- Versatile Algorithm Support: XIP3030H supports SHA-3-224/256/384/512, SHAKE-128/256, and cSHAKE-128/256. That is, XIP3030H covers all algorithms defined in [1] and also all algorithms included in [2] are supported via cSHAKE.

- Secure Architecture: The execution time of XIP3030H is independent of the input values and, consequently, provides full protection against timing-based side-channel attacks.

- Standard Compliance: XIP3030H is compliant with FIPS 202 [1] and SP 800-185 [2]. XIP3030H can be used as a part of numerous systems and protocols that require SHA-3 or its derivatives.

- Easy Integration: The 64-bit interface of XIP3030H supports easy integration to various systems.

## **Functionality**

The main functionality of XIP3030H is to calculate a SHA-3 message digest (also commonly known as a hash value). SHA-3 is a family of hash functions that NIST has standardized in FIPS PUB 202 [1] in August 2015.

In addition to basic hash functions SHA-3-224/256/384/512 with outputs (hashes) of different predefined lengths, XIP3030H supports SHAKE-128 and SHAKE-256. They are *extendable-output functions* (XOFs) defined in [1], and they allow a user to query arbitrary-length output data from the functions while maintaining the security levels of 128 and 256 bits, respectively. Additionally, XIP3030H supports also NIST Special Publication 800-185 [2] by supporting cSHAKE-128 and cSHAKE-256 XOFs.

2

The XIP3030H is optimised for high throughput and low latency.

## **Block Diagram**

The internal high-level block diagram of XIP3030H is depicted in Figure 1.

XIP3030H: SHA-3 Datasheet, ver. 1.0

#### Interfaces

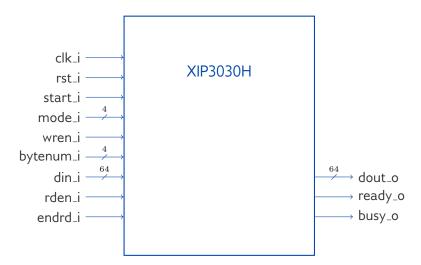

The external interfaces of XIP3030H are depicted in Figure 2.

Figure 2: Interface diagram of XIP3030H.

This Product Brief describes a high-level overview of the functionality and capabilities of XIP3030H. Please contact sales@xiphera.com for a complete datasheet with a detailed description of the input and output signals, startup procedure of XIP3030H, example simulation waveforms, and the FPGA resource requirements of your targeted FPGA family.

#### FPGA Resources and Performance

Table 1 presents the FPGA resource requirements for representative implementations on different FPGA architectures. On request, the resource estimates can also be supplied for other FPGA families. For in-depth perfomance figures please request and consult the datasheet.

| Device                                                     | Resources  | $f_{MAX}$  | Max. throughput* |

|------------------------------------------------------------|------------|------------|------------------|

| Intel® Agilex® F <sup>†</sup>                              | 5170 ALM   | 583.77 MHz | 37.36 Gbps       |

| Intel <sup>®</sup> Stratix <sup>®</sup> 10 GX <sup>†</sup> | 5166 ALM   | 344.12 MHz | 22.02 Gbps       |

| Xilinx® Versal® Prime <sup>‡</sup>                         | 6330 LUT   | 492.37 MHz | 31.51 Gbps       |

| Xilinx® Virtex® UltraScale+‡                               | 6908 LUT   | 651.89 MHz | 41.72 Gbps       |

| Xilinx <sup>®</sup> Zynq <sup>®</sup> MPSoC <sup>‡</sup>   | 6921 LUT   | 527.70 MHz | 33.77 Gbps       |

| Lattice® Certus-NX® §                                      | 11634 LUT4 | 108.28 MHz | 6.93 Gbps        |

| Lattice <sup>®</sup> ECP5 <sup>®</sup> ¶                   | 11742 LUT4 | 49.27 MHz  | 3.15 Gbps        |

Table 1: Resource usage and performance of XIP3030H on representative FPGA families.

3

$<sup>^*</sup>Throughput = \frac{1088}{17} * f_{MAX};$  for SHA3-256 mode.  $^\dagger$ Quartus $^\otimes$  Prime Pro 21.1.0, default compilation settings, industrial speedgrade.

<sup>&</sup>lt;sup>‡</sup>Vivado 2021.1, default compilation settings, industrial speedgrade.

<sup>§</sup>Radiant 3.2.1, default compilation settings, synthesised with Synplify.

<sup>&</sup>lt;sup>¶</sup>Diamond 3.12.0, default compilation settings, synthesised with Synplify.

XIP3030H: SHA-3 Datasheet, ver. 1.0

## Ordering and Deliverables

Please contact sales@xiphera.com for pricing and your preferred delivery method. XIP3030H can be shipped in a number of formats, including netlist, source code, or encrypted source code. Additionally, a comprehensive VHDL testbench and a detailed datasheet are included.

## **About Xiphera**

Xiphera specializes in secure and efficient implementations of standardized cryptographic algorithms on Field Programmable Gate Arrays (FPGAs) and Application Specific Integrated Circuits (ASICs). Our product portfolio includes individual cryptographic Intellectual Property (IP) cores, as well as comprehensive security solutions built from a combination of individual IP cores.

Xiphera is a Finnish company operating under the laws of the Republic of Finland, and is fully owned by Finnish citizens and institutional investors.

#### **Contact**

Xiphera Oy Otakaari 5 FIN-02150 Espoo Finland sales@xiphera.com +358 20 730 5252

#### References

- [1] NIST Computer Security Division. SHA-3 Standard: Permutation-Based Hash and Extendable-Output Functions. FIPS Publication 202, National Institute of Standards and Technology, U.S. Department of Commerce, August 2015.

- [2] John Kelsey, Shu jen Chang, and Ray Perlner. SP 800-90A Rev.1 Recommendation for Random Number Generation Using Deterministic Random Bit Generators. Technical report, National Institute of Standards & Technology, Gaithersburg, MD, United States, 2015.